Оглавление:

- Техническое задание

- Введение в "Вектор 06ц"

- Краткое описание

- Центральный процессор

- Сигналы, с которыми работает МП, и их назначение

- Управление прямым доступом к памяти (захватом)

- ОЗУ

- Куда более интересная задача – использовать в качестве ОЗУ статическую память!

- ПЗУ объемом 8 кБ К573РФ4 ("Гепард")

- Прочие основные узлы ЭВМ

- Глоссарий

- ОЗУ

- Использование статической памяти

- Приложение. Справочные данные

Задача передо мною какая-то поставлена, но еще толком не

сформирована, суть ее примерно такая: собрать

нечто наподобие "Вектора 06ц", недокомпьютер

по современным меркам. В "нечто" должно быть применено минимум деталей, но без всяких ПЛИС.

Ну можно и с ПЛИС, но с самой простецкой. Но надо такое, чтоб с возможностью запуска операционной системы CP/M,

и баловаться :) Задача - не тривиальная, а то, что она поставлена передо мной именно мною же, делает ее не очень скромной

и практически не выполнимой.

Важно: в техническом описании номера элементов указаны как на схеме v06c_ck_page1.jpg

краткое описание:

- Процессор: КР580ВМ80А, работает на повышенной тактовой частоте 3 МГц (стандартная максимальная частота 2.5 МГц);

- ОЗУ: 64 КБ, из которых до 32 КБ может использоваться под видеопамять;

- ПЗУ: 512 байт или 2 КБ; содержит только начальный загрузчик;

- Звук: Трехголосный синтезатор звука, выполнен на микросхеме программируемого таймера КР580ВИ53;

- Аппаратная прокрутка экрана;

- Возможность расширения через системную шину и порты ввода-вывода;

Процессор - КР580ВМ80А (КР580ИК80, .). Клон и полный аналог МП Intel 8080A (1974 год). Имеет раздельные 16-разрядную шину адреса

и 8-разрядную шину данных.

В системе команд 80 (по другим источникам, 78): 16 команд передачи данных, 31 команда для их обработки,

28 команд для перехода (с прямой адресацией), 5 команд управления. 244 кода операций. Конструктивно

помещен в пластиковый корпус с 40 выводами.

КР580ВМ1 – значительно улучшенная и более быстрая версия КР580ВМ80А. Прямых зарубежных аналогов нет.

Штатное одинарное питание +5 В. Частота до 5 МГц.

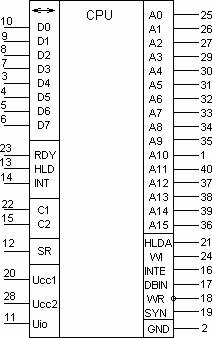

Рис B.

Интегральное исполнение

ИМС КР580ВМ80А.

Сигналы, с которыми работает МП, и их назначение:

A0-A15 - выходные сигналы Шины Адресов (ША). Предназначена для передачи адреса ко всем

периферийным устройствам (как к устройствам памяти, так и к портам ввода/вывода);

D0-D7 - входные или выходные сигналы двунаправленной Шины Данных для обмена данными с

памятью или портами ввода/вывода, а также для вывода из микропроцессора информации о его состоянии;

C1 (22), C2 (15) - входные периодические сигналы для тактирования микропроцессора;

SYN, SVNC (19) - выходной сигнал синхронизации, вырабатываемый в начале каждого машинного

цикла и указывающий, что по шине данных передается информация о состоянии микропроцессора;

R - входной сигнал установки микропроцессора в начальное состояние, обеспечивающее выполнение

программы с команды, содержащейся в ячейке памяти с адресом 0000Н;

ПМ - выходной сигнал высокого уровня, подтверждает готовность МП к приему данных и тем самым

инициирует выдачу данных периферийными модулями на шину данных;

ВД - выходной сигнал, сопровождающий выдачу микропроцессором информации на шину данных для

записи в периферийные модули;

Для синхронизации процессора с памятью и внешними устройствами, имеющими меньшее

быстродействие, для организации прямого доступа к памяти и останова процессора предусмотрены

три специальных состояния: ОЖИДАНИЕ, ЗАХВАТ и ОСТАНОВ, длительность которых произвольная, но всегда кратная Т.

ГТ - входной сигнал от модулей памяти или портов ввода-вывода, указывающий на их готовность к обмену данными с

микропроцессором;

ОЖ - выходной сигнал при ожидании микропроцессором готовности периферийных модулей, шин адресов и данных

микропроцессора ввысокоимпедансное состояние

ЗХ - входной сигнал, инициирующий перевод шин адресов и данных микропроцессора в высокоимпедансное состояние;

ПЗХ - выходной сигнал, подтверждающий перевод шин адресов и данных микропроцессора в высокоимпедансное состояние;

Управление прямым доступом к памяти (захватом):

HLD - входной сигнал запроса на захват шин Д7...Д0, А15...А0 со стороны внешних устройств. Процессор

переходит в состояние "ЗАХВАТ", и системная шина может использоваться внешними устройствами;

HLDA - выходной сигнал подтверждения захвата шин. Является признаком допуска внешнего

устройства к шинам данных и адреса системы.

INTE - выходной сигнал разрешения прерывания высокого уровня, указывающий, что процессор готов

к обмену (может принять запрос прерывания). После перехода к обслуживанию прерывания на выходе

устанавливается сигнал низкого уровня и запросы прерывания не воспринимаются.

INT - входной сигнал запроса прерывания работы процессора, поступающий от внешних устройств

Шина данных D0-D7 предназначена для передачи данных от микропроцессора к периферийным устройствам и обратно.

Шина адреса предназначена для передачи адреса ко всем периферийным устройствам (как к устройствам памяти, так

и к портам ввода/вывода).

В шину управления условно объединяют набор линий, передающих различные управляющие сигналы от процессора на все

периферийные устройства и обратно. обязательно присутствует линии, передающие

следующие сигналы:

- RD - сигнал чтения

- WR - сигнал записи

- MREQ - сигнал, инициализации устройств памяти (ОЗУ или ПЗУ)

- IORQ - сигнал инициализации портов ввода/вывода

Кроме того, к сигналам шины управления относятся:

- READY - сигнал готовности

- RESET - сигнал сброса

И еще несколько специальных сигналов.

Оперативное Запоминающие Устройство (ОЗУ)

Предназначено для приема, хранения и передачи данных по запросу процессора или контроллера дисплея.

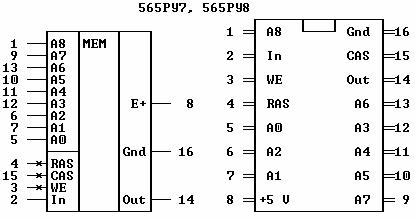

ОЗУ реализовано на 32 микросхемах К565РУ6Г емкостью 16К*1разряд (т.о. всего 65536 байт памяти), а также 4 микросхемах

К155КП2 и одной К155РЕ3

К565РУ6Г - микросхема памяти динамического типа (DRAM - требуется

регенерация записанной информации). Емкость микросхемы - 16k*1.

В состав ОЗУ входят следующие устройства:

- Формирователь сигнала выборок линеек ОЗУ - D37 [К155РЕ3];

- Мультиплексор адреса - D11-D14 [К155КП2];

- Мультиплексор данных - D41-D44 [К155КП2];

- Блок памяти - D49-D80 [32 МС К565РУ6Г].

Прочие основные узлы ЭВМ

Двунаправленные шинные формирователи D1, D19 обеспечивают буферизацию шины данных и старшего

байта адреса

Элементы, применяемые в оригинальном Вектор-06ц согласно схемы v06c_ck_page1.jpg:

| D1-КР580ВМ80А |

ЦПУ |

| D2-КР580ВА86 |

Двунаправленный 8-разрядный шинный формирователь с повышенной нагрузочной способностью |

| D3-КР1533ЛА1 |

Два логических элемента 4И-НЕ |

| D4-КР580ВА87 |

Отличается от КР580ВА86 [D2] тем, что двунаправленная передача осуществляется с инверсией |

D5-КР556РТ18

[HM76161] |

Однократно программируемое ППЗУ. Имеет организацию 2Kx8. ТТЛШ |

D6-D9

К155КП2 |

Cдвоенный селектор-мультиплексор 4-1 с общими входами выбора данных и раздельными входами стробирования |

D10-D41

К565РУ6Г |

Микросхемы памяти динамического типа с организацией 16k*1 |

| D42-КР1533ИЕ7 |

4-разрядный двоичный реверсивный счетчик |

| D43-D46-КР1533КП12 |

2-разрядный 4-канальный коммутатор с тремя устойчивыми состояниями по выходу |

| D50-D53-К555 |

|

| К155РЕ3 |

|

| D1-КР580ВА87 |

Двунаправленный 8-разрядный шинный формирователь с повышенной нагрузочной способностью и инвертирующим выходом |

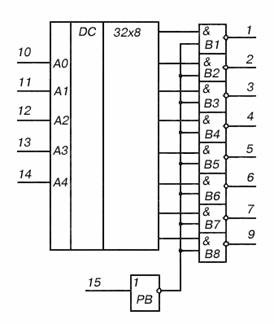

| D36-К155РЕ3 |

Формирователь временных диаграмм модуля электронного (МЭ) [системного модуля]. Электрически программируемое

посредством пережигания плавких перемычек постоянное запоминающее устройство (ППЗУ) емкостью 256 бит (32x8). В

исходном состоянии (на заводе?) по всем адресам и разрядам записан логический ноль |

D37-К155РЕ3

[S8223] |

Формирователь сигнала выборок линеек ОЗУ |

К155РЕ3

Электрически программируемое посредством пережигания плавких перемычек постоянное запоминающее устройство.

|

1 - выход B1;

2 - выход B2;

3 - выход B3;

4 - выход B4;

5 - выход B5;

6 - выход B6;

7 - выход B7;

8 - общий;

9 - выход B8;

10 - вход адресный A0;

11 - вход адресный A1;

12 - вход адресный A2;

13 - вход адресный A3;

14 - вход адресный A4;

15 - вход разрешения выборки PB;

16 - напряжение питания;

|

К155РЕ3 работает так:

Глоссарий

Дешифратор

Шина адреса МП

ЗУ - запоминающее устройство

ЗУПВ - ЗУ с произвольной выборкой

ИМС - интегральная микросхема

МП - микропроцессор

МЭ - модуль электронный

УГО - условное графическое обозначение

Приложение 1. Справочные данные

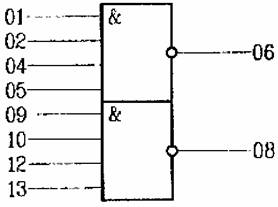

Условное

графическое обозначение мс КР1533ЛА1 Условное

графическое обозначение мс КР1533ЛА1

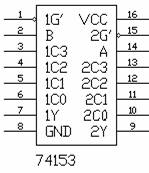

Микросхема К155КП2 представляет собой сдвоенный селектор-мультиплексор 4-1 с общими входами выбора

данных и раздельными входами стробирования. При высоком уровне напряжения на входе стробирования V соответствующий выход

A/D устанавливается в состояние низкого уровня напряжения, в ином случае на выход приходит информация от выбранного

входами S1, S2 информационного входа A/D0-A/D3

Мультиплексор

Назначение мультиплексоров (от английского multiplex - многократный) - коммутировать в заданном порядке сигналы,

поступающие с нескольких входных шин (входов) на одну выходную. У мультиплексора может быть, например, 16 входов и 1 выход.

Это означает, что если к этим входам присоединены 16 источников цифровых сигналов - генераторов последовательных цифровых слов,

то байты от любого из них можно передавать на единственный выход. Для выбора любого из 16 каналов необходимо иметь 4 входа

селекции (24=16), на которые подается двоичный адрес канала. Так, для передачи данных от канала номер 9 на входах

селекции необходимо установить код 1001. В силу этого мультиплексоры часто называют селекторами или

селекторами-мультиплексорами.

Количество мультиплексируемых входов называется количеством каналов мультиплексора, а количество выходов называется

числом разрядов мультиплексора.

Разрешающие входы используют для расширения функциональных возможностей мультиплексора. Они используются для

наращивания разрядности мультиплексора, синхронизации его работы с работой других узлов. Сигналы на разрешающих

входах могут разрешать, а могут и запрещать подключение определенного входа к выходу, то есть могут блокировать

действие всего устройства

Основные типы входов мультиплексоров:

1) информационные (обозначаются как Si, xi, Di);

2) управляющие (иначе - селекторные, адресные).

Микросхема К155КП2 [КМ155КП2] представляет собой сдвоенный селектор-мультиплексор 4 канала на 1 с общими

входами выбора данных A, B.

Кроме указанных входов мультиплексор имеет еще стробирующие (разрешающие) входы 1G’, 2G’.

При высоком уровне напряжения на входе стробирования 1G’/2G’ соответствующий выход 1Y/2Y

устанавливается в состояние низкого уровня напряжения, в ином случае на выход приходит информация от выбранного

входами A, B информационного входа 1C0-1C3 и 2C0-2C3.

| Номер вывода |

Обозначение |

Назначение |

| 1 |

1G’ |

вход стробирования (разрешения) |

| 2 |

B |

вход выборки разряда |

| 3 |

1C3 |

вход информационный |

| 4 |

1C2 |

вход информационный |

| 5 |

1C1 |

вход информационный |

| 6 |

1C0 |

вход информационный |

| 7 |

1Y |

выход |

| 8 |

GND |

общий |

| 9 |

2Y |

выход |

| 10 |

2C3 |

вход информационный |

| 11 |

2C2 |

вход информационный |

| 12 |

2C1 |

вход информационный |

| 13 |

2C0 |

вход информационный |

| 14 |

A |

вход выборки разряда |

| 15 |

2G’ |

вход стробирования (разрешения) |

| 16 |

VCC |

напряжение питания +5В |

В некоторых сериях, например К1533КП15, имеется вход управления установки выходов мультиплексора

в третье состояние (обозначается как EZ). Некоторые мультиплексоры, например К155КП7, имеют два выхода,

при этом один из них соответствует инвертированному значению заданной функции, другой - прямому.

Таблица истинности К155КП2, КМ155КП2

| Входы | Выход |

| S0

| S1

| 0

| 1

| 2

| 3

| V

| | X

| X

| X

| X

| X

| X

| 1

| 0

| | 0

| 0

| 0

| X

| X

| X

| 0

| 0

| | 0

| 0

| 1

| X

| X

| X

| 0

| 1

| | 1

| 0

| X

| 0

| X

| X

| 0

| 0

| | 1

| 0

| X

| 1

| X

| X

| 0

| 1

| | 0

| 1

| X

| X

| 0

| X

| 0

| 0

| | 0

| 1

| X

| X

| 1

| X

| 0

| 1

| | 1

| 1

| X

| X

| X

| 0

| 0

| 0

| | 1

| 1

| X

| X

| X

| 1

| 0

| 1

|

Применение мультиплексоров в ОЗУ

Мультиплексирование многоразрядного адреса микросхем памяти;

Последовательный опрос многих переменных, датчиков и других однобитовых источников информации;

временное уплотнение аналоговых сигналов в телефонии;

мультиплексирование выходных данных тестопригодных БИС;

построение многоканальных коммутаторов, осциллографов.

Воробьев Н.В. Мультиплексоры // Chip News. - 1998. - № 11-12. - С. 38-41.

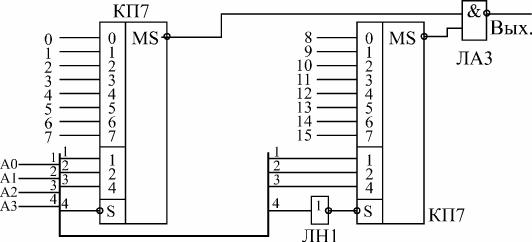

Объединение мультиплексоров для увеличения количества каналов

Старший разряд кода будет выбирать один из двух мультиплексоров! И сигнал будет только с одного из его входов, младщий

будет отключен

Объединение мультиплексоров для увеличения количества каналов

Старший разряд кода будет выбирать один из двух мультиплексоров! И сигнал будет только с одного из его входов, младщий

будет отключен

Сцепленные в кучу мультиплексоры выдают 1 байт в память.

В адресном пространстве ОЗУ для хранения информации, выводимой на экран, отведена зона с адресами 8000H-FFFFH.

При обращении контроллера дисплея к ОЗУ считывается информация из старших 32 Кбайт. Это реализовано подачей

постоянного высокого уровня сигнала на вход 05 мультиплексора адреса D14.

Мультиплексор адреса D11...D14 управляется сигналами "MX1", "MX2". Двунаправленные шинные формирователи D1, D19

обеспечивают буферизацию шины данных (D19) и старшего байта адреса (D1).

Значительный эффект в производительности однопроцессорной системы дает разделение ОЗУ на несколько

модулей, функционально самостоятельных, что позволяет им работать независимо друг от друга. Производительность

увеличивается за счет уменьшения простоев устройств из-за так называемых конфликтов при обращении к ОЗУ.

При параллельной работе многих устройств ввода-вывода и процессора неизбежны ситуации, когда нескольким

устройствам требуется обращение к ОЗУ для записи или чтения информации. Такая ситуация и называется конфликтной.

Естественно, разрешить этот конфликт можно только путем введения системы приоритетов, которая устанавливает

определенную очередность удовлетворения запросов в ОЗУ. При этом неизбежны очереди, а следовательно, и простои

устройств, не имеющих высшего приоритета. В наибольшей степени от этого страдает процессор, так как по принципу

своей работы он может ожидать в очереди обслуживания сколь угодно долго, в то время как большинство периферийных

устройств, в основном электромеханических, ждать долго не могут или это будет приводить к слишком большим потерям

времени. Так, например, если вовремя не считать информацию с накопителя на магнитном диске, то придется потерять

несколько миллисекунд (один оборот диска) до следующего момента, когда эта информация может быть считана. При наличии

нескольких модулей ОЗУ с независимым управлением есть определенная вероятность того, что различные устройства будут

обращаться к различным модулям, а следовательно, очередь к ОЗУ разделится на несколько меньших очередей и время

ожидания (т. е. простой устройства) в очереди будет уменьшено. Кроме совмещения во времени различных этапов обработки

информации в системах класса ОКОД существенное увеличение производительности достигается за счет введения конвейерной

обработки, точнее конвейера команд.

|